MAY 2026

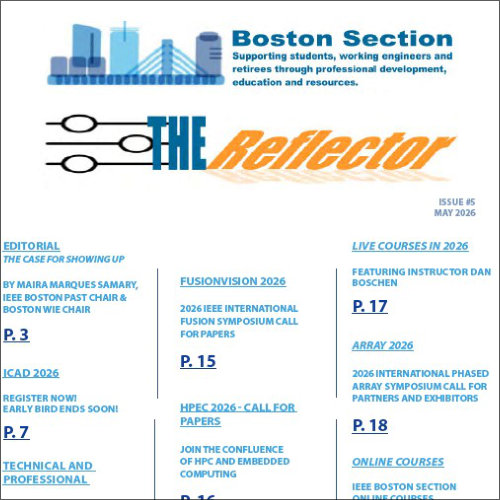

The Reflector

Read about what’s happening in the Boston Section including words from our leadership, meeting notices, courses and more.

June 2026

Call for Sponsors!

Don’t miss the opportunity to get involved in this exciting AI Conference now in its second year. 100+ paper presentations, industry speakers and innovative panel discussions.

2026 IEEE Boston Conferences

We’re hosting 5 technical conferences in 2026: ICAD, FusionVision, HPEC, URTC and ARRAY. What a year!

UPCOMING EVENTS

IEEE Canada Blockchain Forum 2026 (4th edition)

Recent News and Announcements

The Case for Showing Up

Maira Marques Samary, Boston Section Past Chair, shares her perspective on why getting involved is important the value of networking and how we benefit as individuals and as a community.

2026 Boston Section Awards Honorees

See who was honored at the 2026 Boston Section Awards including IEEE Medalists, IEEE Fellows and IEEE Boston Section Award winners.

Space Day at the JFK Library on April 21

Join Francesca Scire-Scappuzzo, PhD, moderating “How we reach the sky,” the opening panel at Massachusetts Space Day at the JFK Library on April 21, 2026 (10:30AM – 11:00AM)

Around Your Region

Denise Griffin, IEEE Region 1 Northeastern Area Chair, describes her involvement with the Region and what resources that offer to our members.

Boston Section Awards Celebration

Please register now to join us at the Boston Section Awards at Tufts University on Sunday 3/22. We’ll socialize, enjoy food and beverages and most importantly, recognize our amazing volunteers.

The Benefits of Online and On-Demand Training with IEEE Boston

1

Expert

Trainers

Online training with an expert gives learners from anywhere in the world high-quality instruction from seasoned professionals.

2

On-Demand Access

With on-demand course offerings, students learn at their own pace, allowing them to revisit topics as needed.

3

Online

Support

Dedicated online support ensures that learners receive prompt assistance.